索尼PSV遭拆解 发现竟内置3D技术芯片

去年年末索尼发布了他们的PSV,而它也很快被iFixit(注:国外一个著名的IT产品拆解网站)和其他组织拆解了。经过对其内部的硬件进行详细的探究,发现了一些大家未知的东西,比如内存大小跟之前宣称的不一致等,而最大的发现莫过于PSV使用了索尼东芝联合开发的TSVs(Si贯通电极)标准和栈叠芯片 SiP – 一种3D技术,其中TSVs标准目前还没有其他商业设备开始使用。以下是原文:

我们在内部发现了常规的配套无线芯片,动作感应器和内存,不过PSV出众表现的核心来源还是索尼的CXD5315GG处理器;PSV配备了一个四核ARM Cortex-A9处理器,内置了一个四核GPU——SGX543MP4+图形处理单元。

上文中我说我们发现了内存,不过实际上我们在主板上找到的唯一独立内存是4G的东芝闪存,而索尼的说明却声称有512M(4GB)的常规只读内存,外加128MB(1GB)的显存。在手机里,我们通常会发现内存是在一个封装叠加(PoP)的构造中,移动SDRAM在顶部,而处理器会在底部。

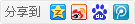

然而,当我们把(PSV)的那一部分从主板上拿下来并做一系列X光测试后,侧边的成像证明我错了——它是栈结构的,而成像照片表明,在那儿看起来有5个电路片,一个厚电路片在底部,一个薄电路片直接在顶部,而另有三个小电路片在它的顶部。下方的第二个电路片可能是一个衬片,因为似乎并没有连接线通往这里。

这马上让我们有了一个猜测——如果上方的第二个电路片是显存的话,它是宽型I/O DRAM,而且它还使用了Si贯通电极(TSVs)了吗?是时候做一个横截面检查来找出真相了,而这也几乎预示着我们要失望了:

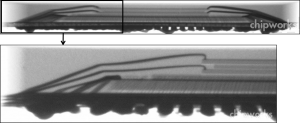

这种面对面的连接可以回溯到2006年Sony原始的PSP上,东芝把它称为“半内置式DRAM”,现在他们称它为“栈叠式芯片SoC”。球间距是令人印象深刻的45微米标准,几乎和TI的铜柱一样紧密,不过它们排列后是为了达到40微米的间距。

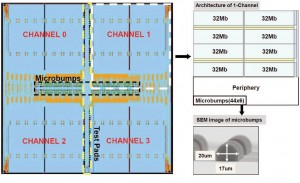

那么在栈结构里的那五个芯片到底是什么呢?在底部我们知道有处理器芯片,与它面对面的是一个三星1Gb宽的I/O SDRAM,顶部的三个电路片包括了两个三星2Gb的移动DDR2 SDRAM和一个将它们隔开的衬片,而且依照惯例,它们有相互的连接线。底部的电路片是250微米标准的厚度,而其他的是100~120微米的标准。

当我们查看处理器和1Gb内存照片时,我们可以发现它们被故意设置成栈结构,因为这两者的中心都是一排匹配的线路焊点。

进一步的检查揭示了在这两块区域各有540个(总计达1080个)焊点(2个子区域各包含45排6焊点阵),所以可能是2 x 512 bit I/O运算,再被细分成4 x 128的运算。

去年在ISSCC(国际电子电路研讨会)上三星描述了一个使用TSVs的相似的宽型I/O DRAM,声称数据带宽达到12.8Gb/s,四倍于相同LPDDR2部件的带宽。我怀疑作者希望他们的设计在年底前就能应用于一个批量消费设备上,而这似乎真的发生了!

这个设备使用了相似的I/O,不过并不完全相同,JEDEC宽度I/O标准在今年的早些时候才发布(它每一部分需要50排的6焊点阵),当然它的发布提早了一年。

正如我们所看到的,通过把处理器和不同的内存组合在Vita的同一个封装包里,索尼和东芝生产了为数不多的真正的SiP部件。而我会称它为3D,尽管行业大会目前规定这项应该被称为“TSV基础部件”——所以用我们当前的行话来说,它不是3D。

这个设备凸显了将TSV引入SiP世界的商业障碍,因为不仅相关部件需要设计成满足I/O标准,而且双栈构造技术至少也需要基本成熟;所以表现的好坏与否完全取决于第三个和更多的电路片是否能满足TSVs标准。不可否认的是,对移动设备的要求正以令人吃惊地速度增长,不过似乎还需要过一段时间我们才能在商业设备上看到TSVs。时间会说明一切!