3D新闻:全球首款异构 3D FPGA高端器件

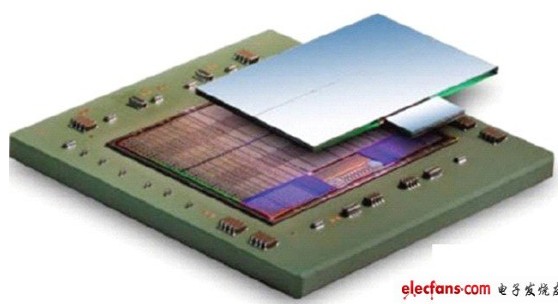

最新3D新闻,继 Virtex-7 2000T 之后,赛灵思日前又推出一款 7 系列的高端器件 Virtex-7 H580T,这是全球首款异构 3D FPGA,该技术是在堆叠硅片互联(SSI)技术的基础上,对 FPGA 和 28Gbps收发器的整合方式进行了创新。赛灵思亚太区市场及销售副总裁杨飞表示,从处理器到数模混合再到 IP 资源的整合,赛灵思提供的已经不仅仅是 FPGA 器件,而是 AllProgrammable的平台。

从性能上看,Virtex-7 HT 系列是业界带宽最高的 FPGA,最多可提供16个28Gbps 收发器和72个13Gbps 收发器,也是唯一能满足关键 Nx100G 和400G 线路卡应用功能要求的单芯片方案。首先供货的 Virtex-7 H580T 拥有8个28Gbps 收发器,该器件结合了赛灵思先进的100G 变速机制(gearbox)、以太网 MAC、OTN 和 Interlaken IP,可为客户提供不同的系统集成,从而满足他们在向 CFP2光学模块转型时对密度、功耗和成本的要求。 那么,Virtex-7 H580T和 Virtex-7 2000T 究竟有哪些不同呢?杨飞表示,同样是3D 工艺器件,Virtex-7 2000T 是将4片28nm FPGA 管芯堆叠,从而搭建出68亿个晶体管200万门规模的强大器件。在 Virtex-7 2000T 中,高速串行收发器与 FPGA 是同在一个28nm 的 die 上,而28Gbps 收发器在40nm 工艺上表现甚佳,所以目前最理想的做法是采用40nm 的28Gbps 收发器。Virtex-7 HT 器件就是将3片28nm FPGA 管芯(内置72个13Gbps 收发器)和16个40nm 的28Gbps 收发器(共2片,每片8个置于 FPGA 管芯阵列的两侧)进行堆叠互联。从性能上看,Virtex-7 2000T 拥有最高的逻辑资源(适用于原型验证、ASIC 替代和一些前沿应用的算法实现等),Virtex-7 H580T 则在收发器数量和带宽上具有更高的表现,这也与其产品定位有很大关系。

有关人士表示,模拟工艺并不完全能跟随摩尔定律走,赛灵思的异构3D 工艺中,65nm 工艺的金属连接层本身是被动组件,可以自由搭配40nm和28nm 工艺的数字和模拟器件,降低了集成的难度,避免了散热的难题。“从 CFP2光学模块接口要求的抖动特性眼图实测效果看,Virtex-7 H580T 表现完美,”汤立人说,“目前市面上 还未 见有 同样 性能 的器 件, 有号 称可 提供 4个 28Gbps 收 发器 的 FPGA 实 际是 能跑 到25Gbps,并且其眼图表现不好。”Virtex-7 H580T 器件采用异构3D 结构提供独立于核心 FPGA 的28 Gbps 收发器,保证了整体信号完整性并提升了生产力。

杨飞表示,FPGA 和收发器分属数字和模拟的不同工艺,Virtex-7 HT 器件的这种异构化设计使赛灵思能够随意选择核心 FPGA 和28Gbps 收发器芯片,这可以减少28nm 工艺下,搭载高速收发器的 FPGA 的漏电问题带来的影响。另外,异构3D 的结构,使得28Gbps 收发器独立在 FPGA 外,因而噪声隔离效果卓越,实现了最佳的整体信号完整性和系统余量,并加快了设计收敛,加速产品上市进程。

Virtex-7 HT 可以说是为高速和高带宽的通信系统度身定做,如 CFP2模块的线卡。杨飞表示,为了升级网络,解决数据用量的几何级增长带来的挑战,通信产业正在改善光学模块的功耗和端口密度,同时还要降低单位比特的成本,由 CFP 向 CFP2以及未来 CFP4光学模块发展是产业趋势。Virtex-7 HT 是唯一一款能在逻辑容量和 I/O 速率上同时满足更高处理能力线路卡要求的 FPGA 单芯片解决方案,能够满足 Nx100G 和400G 线路卡设计的需求,能支持多达4个 IEEE 100GE gearbox,而且能在同一 FPGA 中选择集成高级调试功能、OTN、MAC或 Interlaken IP,无需独立的 gearbox 和 ASSP 器件。杨飞表示,Virtex-7 H580T 能够在单芯片上实现2×100G OTN 转发器,与其相比,以 ASSP 为基础的方案还有一年多才面世,需要5个器件来实现同等功能,而且功耗至少增加40%,成本增加50%,并且没有差异性。此外,将于明年1季度推出的 Virtex-7H870T 器件已经能够支持400GE(目前唯一的单片方案)16个25Gbps 接口的模块。这样就能降低整体功耗和材料成本,而且能够随着协议的不断变化提供更灵活的方案。

虽然赛灵思所使用的台积电的这种3D 工艺并非排他性技术,但由于涉及器件电路的重新设计和布局,所以并非简单的移植就可用。汤立人表示,简单来讲,要用 SSI 技术,必须将管芯之间的互联由原来的 I/O 口互联(该模式无法满足超大规模器件对效率的要求),更改为由中间的金属互联层进行(互连效果相当于同一个 die,延迟只有1ns),这涉及到设计方法学和整个产品平台策略的革命,非一朝一夕可以完成。赛灵思从2006年开始导入计划,历经5年时间方才大功告成,这意味着其他公司要想使用该技术研产,面临的挑战十分巨大。

上一篇:出色3D扫描仪 白领轻松办公优选[ 06-30 ]

下一篇:家用快门式3D眼镜 首选Hi-SHOCK SH01[ 07-10 ]